Part1-CH4-数字的表达和算数电路

加法器

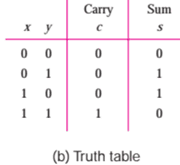

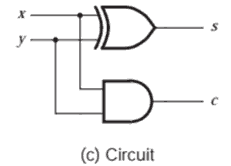

半加法器

半加法器接受两个输入:$x_1,x_2$ 并产生本位和进位两个输出。半加法器的真值表和实现电路如下图所示

|

|

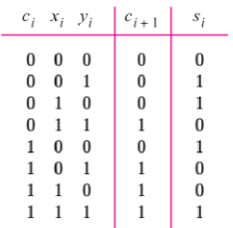

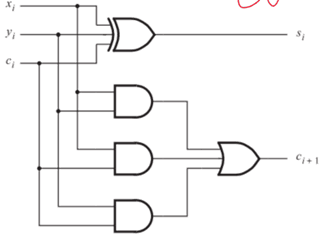

全加法器

全加法器:输入$x_1,x_2,c$,三位(其中c表示上一位到这一位的进位)计算三位相加产生本位和进位。真值表和电路如下

|

|

串行进位全加法器(Ripple-carry Adder)

讲上述全加法器进行串联,前一个的进位输出连接至下一个的进位输入。

原码(True form)反码(1’s complement ) 补码(2’s complement) 在 计算机组成与接口 中有更详细的介绍,此处略去。

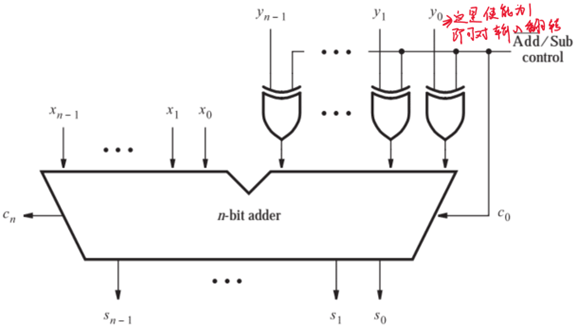

加法(减法)单元

在计算机中,设计专门的减法电路划不来,因此使用补码+加法电路来计算减法。补码的求法是原码取反加一,因此设计如下的计算模块

- 当Add/Sub control 为0时,$y_i=y_i\oplus0=y_i$, 同时输入的基础进位$c_0$等于0。此时是正常调用全加法器计算加法。

- 当Add/Sub control为1时,$y_i=y_i\oplus1=\overline y_i$,同时$c_0=1$。相当于把序列$y$取反后加1(这个加一就是基础进位$c_0$加上来的)算成了补码的形式。故调用全加法器计算减法。

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 風!