毕业设计-阅读笔记2-ADS2193芯片

引入

ADS219X系列芯片是TI公司的低功耗生物电采集模拟前端。最后的X代表几通道,ADS2193就是3通道的的意思。

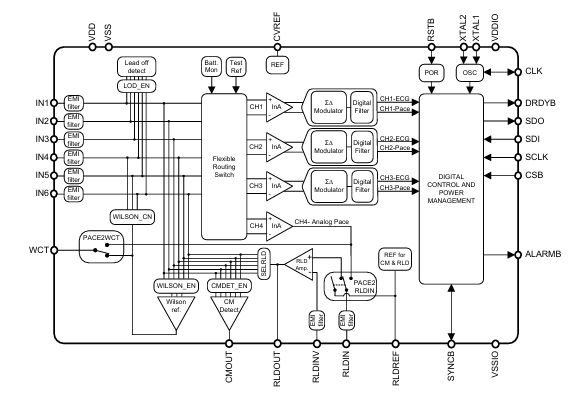

ADS1293具有三个高分辨率通道,最高可达25.6 ksps。每个通道可以独立编程为特定的采样率和带宽,允许用户优化配置的性能和功率。所有输入引脚都包含一个EMI滤波器,可以通过灵活的路由开关路由到任何通道。灵活的路由还允许构建独立的导联,而无需外部重新连接引线。例如右腿驱动和Wilson/Goldberger导联。第四个通道允许外部模拟速度检测,不使用数字速度检测的应用程序。ADS1293集成了一个自诊断报警系统,当系统超出工作条件范围时进行检测。这样的事件会报告给错误标志。错误标志的总体状态在专用的ALARMB引脚上作为信号可用。

关键电气参数

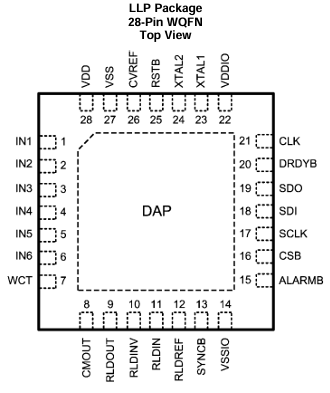

- 采用28-PIN WQFN封装

- 模拟电源: -0.3v ~ 6v

- 数字电源: -0.3v ~ 6v

- 输入引脚电压耐受范围与电流耐受范围: -0.3v ~ VDD+0.3v, 10ma

- 推荐工作温度:-20 ~ 85$^\circ C$

- Digital Voltage Supply 不应超过min(3.6v,VDD)

- 差分输入端量程$\pm400mv$

- 在3.3V供电,$f_{osc}=409.6khz$下,SPI通信最高支持20MHz

引脚作用

| PIN | TYPE | FUNCTION | |

|---|---|---|---|

| IN1-IN6 | 模拟输入 | 心电电极输入 | |

| WCT | 模拟输出 | Wilson导联中心输出(艾氏三角中心)/模拟起搏信道输出 | |

| CMOUT | 输出 | IN口平均电压输出(可编程) | |

| RLDOUT | 模拟输出 | 右腿驱动放大器输出 | |

| RLDINV | 模拟输入 | 右腿驱动反相输入 | |

| RLDIN | 模拟I/O | 右腿驱动放大器正输入/模拟起搏通道输出 | |

| RLDREF | 模拟输出 | 内部右腿驱动参考电压 | |

| SYNCB | 数字I/O | 多芯片同步I/O(多芯片级联,菊花链模式) | |

| VSSIO | 数字电源 | 数字部分地 | |

| ALARMB | 数字输出 | 警告信号 | |

| CSB | 数字输入 | SPI片选信号 | |

| SCLK | 数字输入 | SPI时钟信号 | |

| SDI | 数字输入 | SPI数据输入信号 | |

| SDO | 数字输出 | SPI数据输出信号 | |

| DRDYB | 数字输出 | 数据就绪信号 | |

| CLK | 数字I/O | 内部时钟输出或外部时钟输入,用于多芯片同步 | |

| VDDIO | 数字电源 | 数字部分电源 | |

| XTAL1 | 数字输入 | 外部晶振1 | |

| XTAL2 | 数字输入 | 外部晶振2 | |

| RSTB | 数字输入 | 重置 | |

| CVREF | 模拟I/O | 用于内部参考电压的外部端子,固定串联1uF电容后接地 | |

| VSS | 模拟电源 | 电源地 | |

| VDD | 模拟电源 | 电源供电 | |

| DAP | NC | NC |

模拟前端

3通道ADC

该芯片通过仪用放大器对前几信号进行放大,然后使用sigma-delta modulator配个数字滤波器进行AD转换。仪用放大器增益为3.5倍,最大差分输入为$\pm400mv$,SDM最大输入为$\pm1.4v$

SDM的工作频率可编程位102.4kHz或204.8kHz,后者提供更大的过采样比,提升数据精度,但功耗更大。时钟速率是通过AFE_RES寄存器的FS_HIGH_CHx位进行配置的。

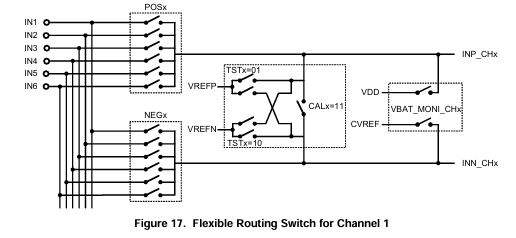

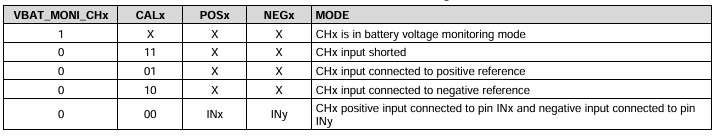

引脚IN1-IN6为ADC输入口,可以通过内部的复用开关配置哪两个为一组。3通道可以进行差分电压测量,也可以通过配置接入Positive Reference或Negative Reference。该芯片支持电池电压检测,但是这个功能将会占用一个通道。

配置的寄存器为:VBAT_MONI_CHx选择是否为电压检测;CALx配置是否连接至片上参考电压;POSx和NEGx选择连接至INx电极。

POS和NEG都占3bit,位于FLEX_CHx_CN寄存器中。

- 000:断开

- 001-110:分别代表IN1-IN6

每个通道的仪用放大器可以通过配置AFE_SHDN_CN寄存器的EN_HIRES_CHx位设置为高性能模式或低功耗模式;SDM可以通过配置同寄存器的SHDN_SDM_CHx位设置为高性能或低功耗模式。低功耗模式将带来3倍的能耗下降。

电池监测

电池监测仅在VDD为2.4v-4.8v时可以使用,5v供电时不能使用。

使用电池监测时需要配置FLEX_VBAT_CN寄存器中的VBAT_MONI_CHx=1来启用,同时必须配置AFE_SHDN_CN寄存器的SHDN_INA_CHx=1来关闭仪用放大器。此时SDM的POSx会连接至VDD,NEGx会采样CVREF引脚的电压。电池电压的计算公式为

除了电池监测模式之外,当VDD小于2.7v时,会触发BATLOW报警,这个报警独立于电池监测模式之外。

测试模式

在FLEX_CHx_CN寄存器中,MSB处有2bit的测试信号选择位。通过对其进行配置,可以对为ADC注入一个内部产生的直流测试信号。

- 00: Test signal disconnected and CH1 inputs determined by POS1 and NEG1 (default)

- 01: Connect channel one to positive test signal

- 10: Connect channel one to negative test signal

- 11: Connect channel one to zero test signal

当连接至0电位测试信号时,ADC输出值为MAX的一半。当连接至正负测试信号时,ADC输出值为$ADC_{out}=[\pm\frac{3.5V_{TEST}}{2V_{REF}}+\frac{1}{2}]ADC_{MAX}$,其中$V_{EST}=V_{REF}/12$

可编程数字滤波器

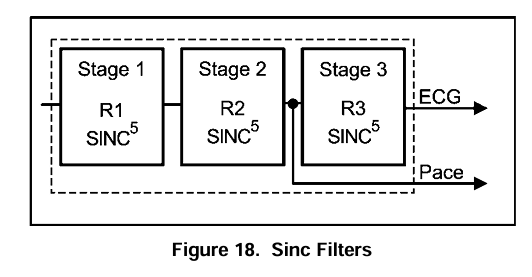

其数字滤波部分由三个可编程的SINC滤波器构成。Sinc滤波器一个全部除去给定带宽之上的信号分量而只保留低频信号的理想电子滤波器,在频域上就是一个矩形窗。

第一级中,标准的抽取率(Decimation rate)为4,也通过R1_RATE寄存器的R1_RATE_Chx位进行配置来变更为2(0:R=4; 1:R=2);为2时,对外输出的数据速率也会翻倍,此时可以更好地获取起搏信号,但是带宽并不改变。

在第二级中,同样地也可以通过配置R2_RATE寄存器设置抽取率为4或2,但是此时更低的抽取率会同时提高输出速率和截止频率的带宽。如果要进行起搏信号检测,推荐将其配置为2.

此时还没有进行很低带宽的滤波,因此第二级输出的信号是包含有起搏信号的。PACE信号会出从这一级输出。

在第三级带宽要低的多得多,对应的也可以设置高的抽取率,抽取率会影响输出数据速率和带宽。每个信道都有一个独立的7bit寄存器来设置R3_RATE_CHx。

- 00000001: 4

- 00000010: 6

- 00000100: 8

- 00001000: 12

- 00010000: 16

- 00100000: 32

- 01000000: 64

- 10000000: 128 (default)

这三级滤波器的配置会影响输出数据速率,ADCMAX的值,滤波带宽。

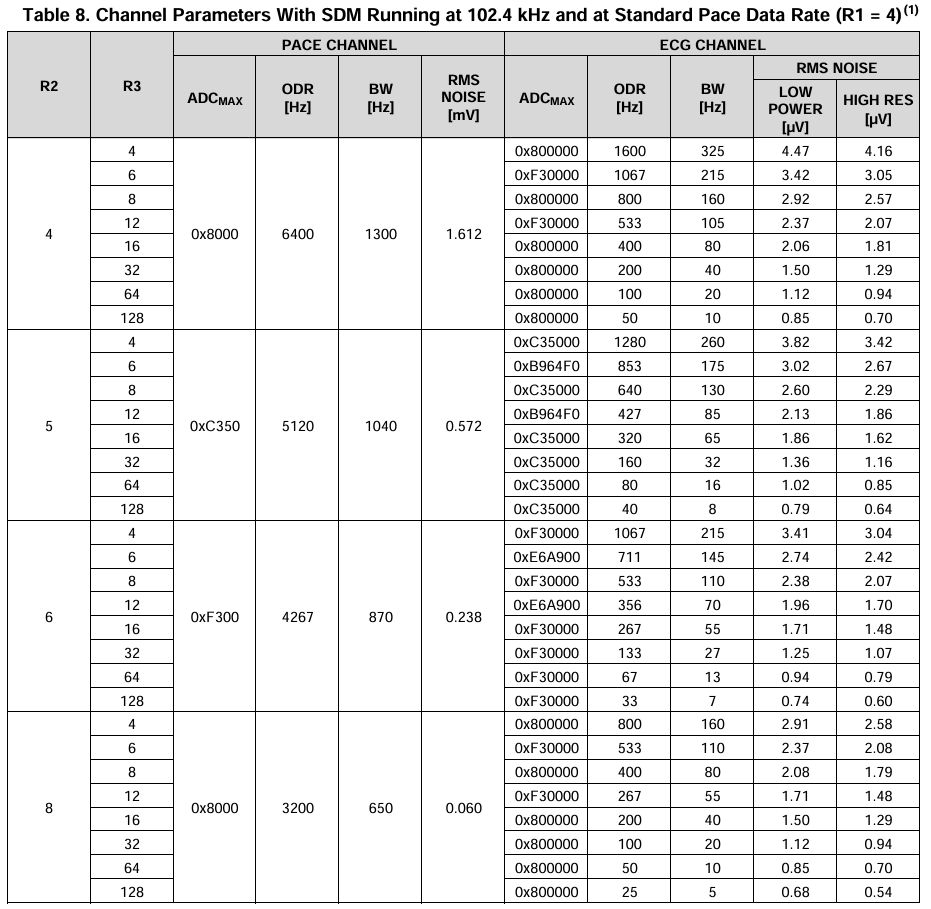

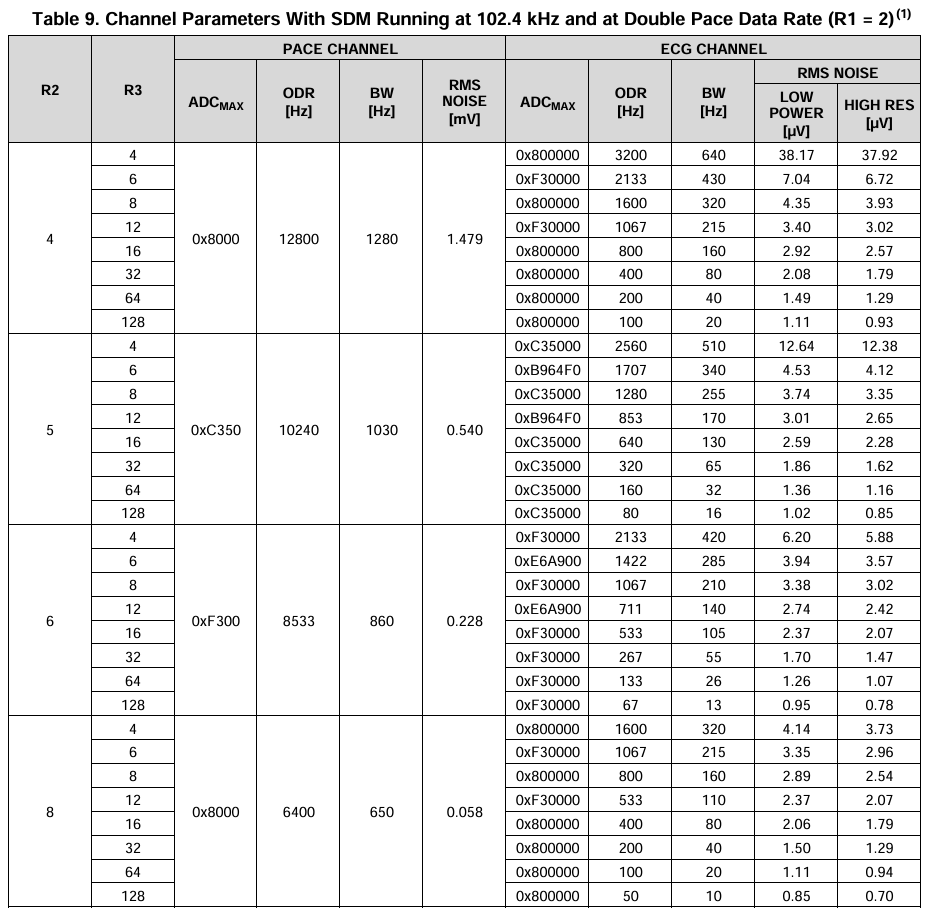

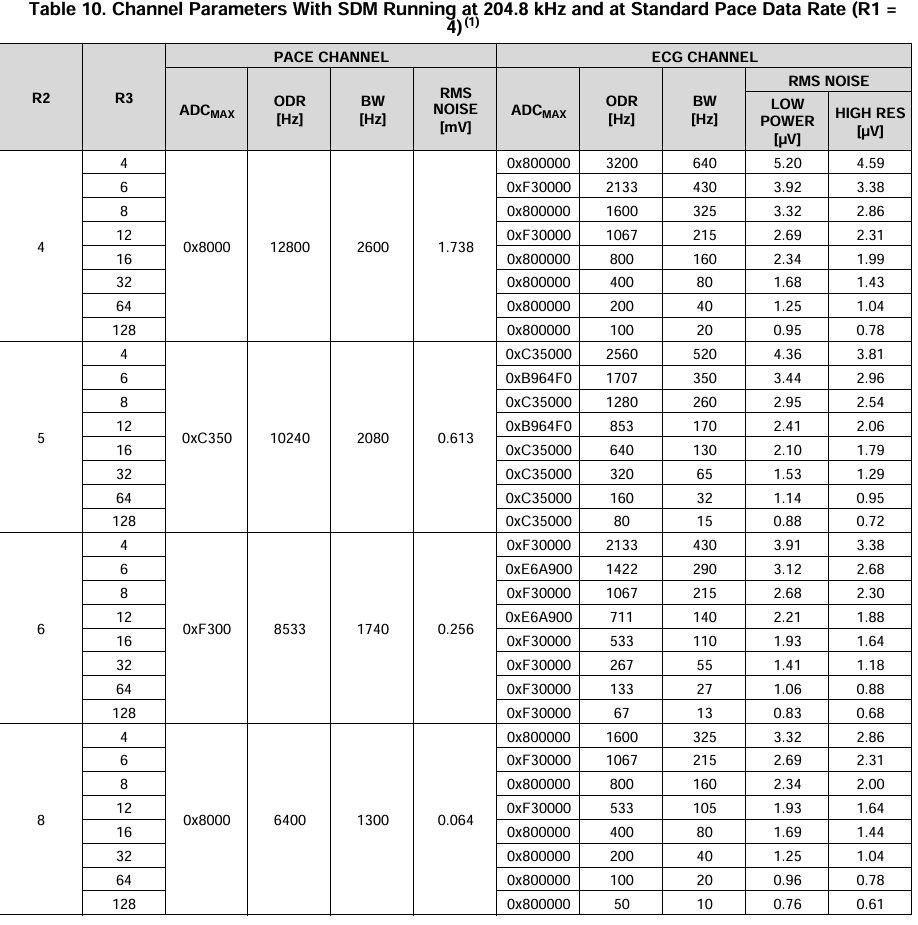

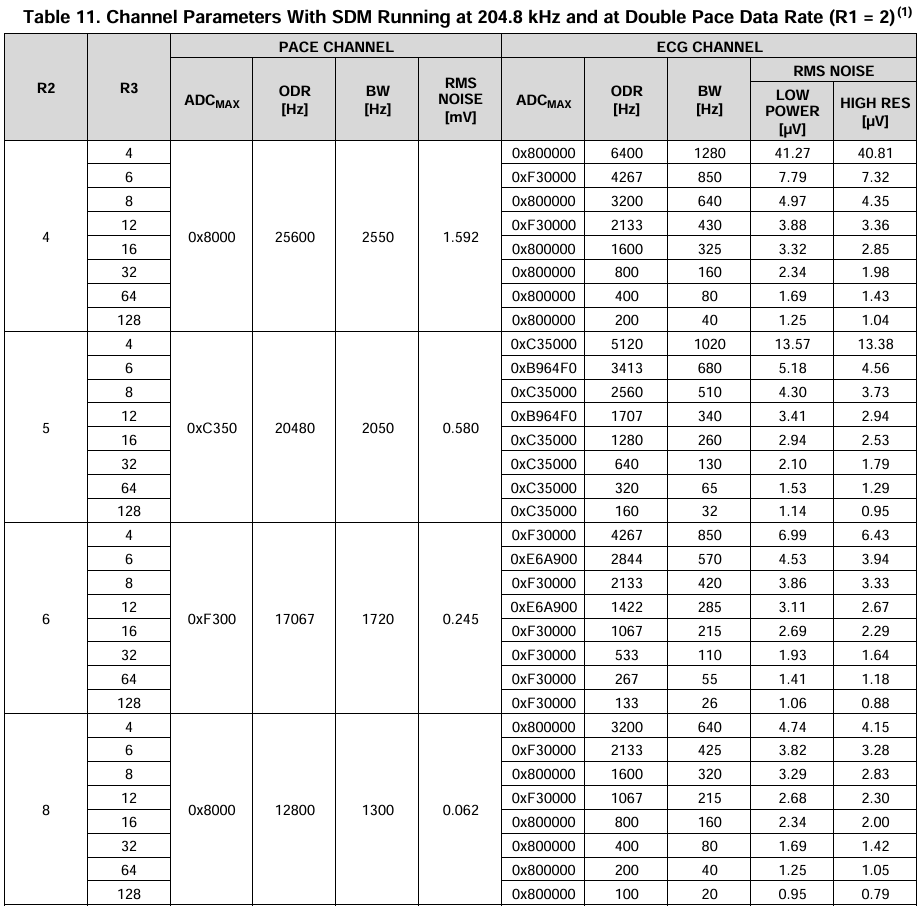

除了这些之外,不同的内部时钟也会影响采样的基频。第二级和第三级以及不同时钟配置下的输出数据速率和带宽如下表:

Wilson中心参考电压

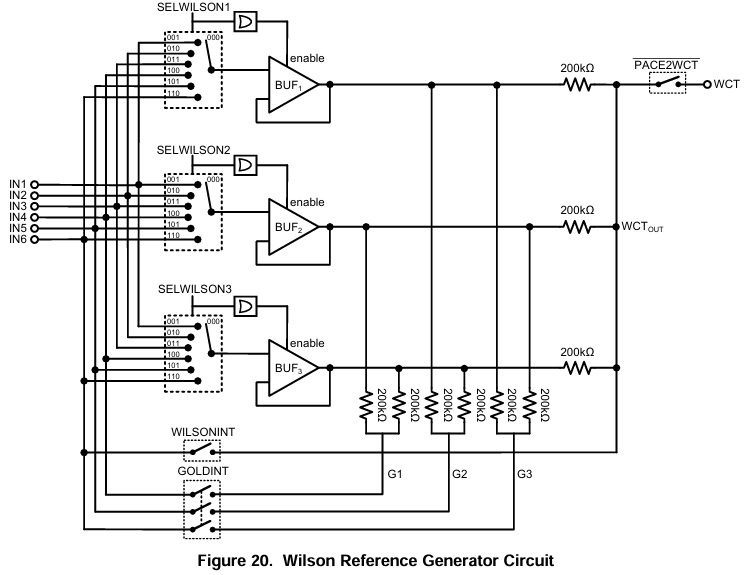

ADS1293的模拟前端自带Wilson中心参考电压的生成电路。如下图所示。该电路由三个Voltage Buffer分别采集LA、RA、LL的电压,后交由平均值电路产生中心电压WCT_OUT.三个Buffer的信号源由WILSON_EN1,WILSON_EN2,WILSON_EN3三个寄存器控制。如果配置为000(NC状态),则Buffer提高阻输入。

WCT_OUT可以被配置输入到IN6和WCT上。只要Analogue Pace Channel没有配置复用到WCT,WCT_OUT就会被输出到WCT引脚上。如果存在复用,也可以通过配置WILSON_CN寄存器的WILSONINTbit使其输出到IN6。

同时,该电路还包含一个对其两两取均值的电路,这可以用于测量aVR,aVL,aVF导联。若BUF1采集LA,BUF2采集RA,BUF3采集LL,通过上图可以看到,$G1=(LA+LL)/2, G2=(RA+LL)/2, G3=(RA+LA)/2$。则$aVR=RA-G1, aVL=LA-G2, aVF=LL-G3$。G参考电压可以被路由到IN4,5,6。

如果想要同时采集单极加压导联和标准导联,则需要多个ads1293芯片协同。

交互指令

芯片通过SPI读写控制寄存器进行交互:数据在CLK下降沿更改,上升沿读取。每条指令由16bit构成,包含8bit指令和8bit数据,如果在16个时钟周期前关闭选片。本芯片SPI不支持双工,在读取时MOSI(SDI)引脚必须保持低电平

- 在8bit指令中,MSB为读写标志位,0为Write Data,1为Read Data

- 若为写模式,则指令发送完后继续发送8bit数据;若为读模式,则指令发送完后待芯片返回8bit数据。

- 在读模式时,可以进行连续读取,首先通过信令发送8bit基地址,继续保持SCLK和CS信号,即可进行连续读取,读取方向为基地址自增。发送完指令后,CS信号需要保持到$8*(1+n)$个时钟周期,其中n为读取的byte数。