STM32的SPI控制器

[施工中..]

SPI控制器

SPI控制器原理

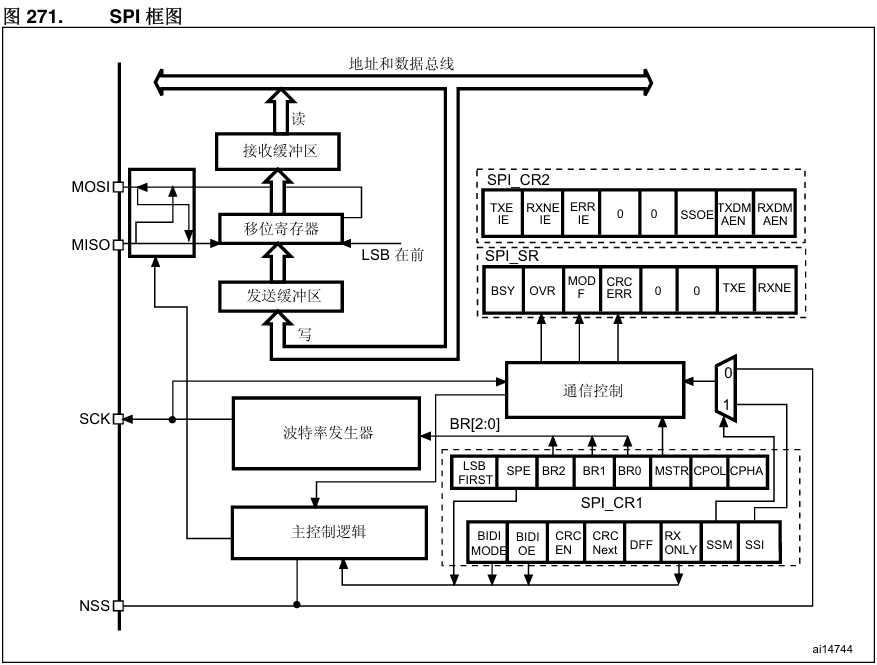

上图展示了STM32F4系列的SPI控制器框图。由波特率发生器产生时间信号,逻辑控制器进行MOSI和MISO控制,并产生片选信号。同时由Tx Rx两个缓冲寄存器+移位寄存器构成发送模块。控制寄存器主要有SPI_CR1,SPI_CR2,BR。

发送流程

- 数据写入Tx Buffer

- Tx Buffer内的的数据填入移位寄存器

- 移位寄存器逐个bit发至MOSI线

- 发送完毕,SPI_SR TXE寄存器置位

接收流程

- 数据写入移位寄存器

- 移位寄存器写入 Rx Buffer

- 接收完成,SPI_SR EXNE置位

- 读取Rx Buffer内的内容

片选信号

在SPI_CR1寄存器中的SSI信号即是该控制器内的片选信号发生器。可通过配置SPI_CR1 SSM寄存器来决定该信号是否对外输出。以此实现不同的片选效果。在NSS对外输出时,配置SPI_CR1 SSOE寄存器又可定义两种不同的硬件管理模式

STM32的SPI控制器支持三种片选模式:

- 软件管理:(SSM=1)外部NSS引脚空闲,可复用其他功能。自定义GPIO通过写高低电平实现片选

- 硬件管理(输出使能模式,SSM=0 SSOE=1):STM32此时为通信主机。当主器件开始通信时,NSS 信号驱动 为低电平,并保持到 SPI 被关闭为止。

- 硬件管理(输出禁止模式,SSM=0 SSOE=0):若STM32此时作为从机模式,则NSS引脚为从机片选输入。若STM32此时作为主机模式,此模式是多主机配置,多主多从SPI极少使用,此处不详细介绍。

时钟极性CPOL

- 0:SCK在空闲时低电平,第一边沿为由低变高

- 1:SCK在空闲时高电平,第一边沿为由高变低

时钟相位CPHA

- 0:SCK在第一(奇数)边沿进行采样

- 1:SCK在第二(偶数)边沿进行采样

时钟极性和相位通常使用00(CPOL=0,CPHA=0)或11的组合。

在使用SPI时,必须讲对应GPIO的引脚设置为复用模式。当在MspInit中进行设置。

SPI相关寄存器

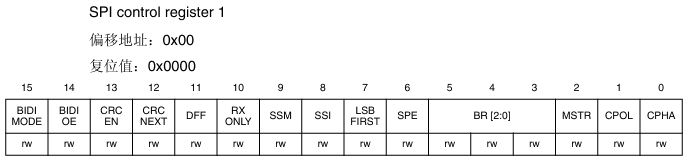

SPI_CR1寄存器

位 15 BIDIMODE:双向通信数据模式使能 (Bidirectional data mode enable)

- 0:选择双线单向通信数据模式

- 1:选择单线双向通信数据模式

位 14 BIDIOE:双向通信模式下的输出使能 (Output enable in bidirectional mode)

此位结合 BIDIMODE 位,用于选择双向通信模式下的传输方向

- 0:禁止输出(只接收模式)

- 1:使能输出(只发送模式)

注意:在主模式下,使用 MOSI 引脚;在从模式下,使用 MISO 引脚

位 13 CRCEN:硬件 CRC 计算使能 (Hardware CRC calculation enable)

0:禁止 CRC 计算

1:使能 CRC 计算

注意:为确保正确操作,只应在禁止 SPI(SPE =“0”)时对此位执行写操作

位 12 CRCNEXT:下一次传输 CRC (CRC transfer next)

0:数据阶段(无 CRC 阶段)

1:下一次传输为 CRC(CRC 阶段)

注意:当 SPI 配置为全双工或只发送模式时,只要最后一个数据写入 SPI_DR 寄存器,就必须对 CRCNEXT 执行写操作。 当 SPI 配置为只接收模式时,必须在接收到倒数第二个数据之后将 CRCNEXT 置 1。 当传输由 DMA 管理时,此位应保持清零状态。

位 11 DFF:数据帧格式 (Data frame format)

0:为发送/接收选择 8 位数据帧格式

1:为发送/接收选择 16 位数据帧格式

注意:为确保正确操作,只应在禁止 SPI(SPE =“0”)时对此位执行写操作

位 10 RXONLY:只接收 (Receive only)

此位结合 BIDIMODE 位,用于选择双线单向模式下的传输方向。此位也适用于多从模式系 统,在此类系统中,不会访问特定从器件,也不会损坏访问的从器件的输出。

0:全双工(发送和接收)

1:关闭输出(只接收模式)

位 9 SSM:软件从器件管理 (Software slave management)

当 SSM 位置 1 时,NSS 引脚输入替换为 SSI 位的值。

0:禁止软件从器件管理

1:使能软件从器件管理

位 8 SSI:内部从器件选择 (Internal slave select)

仅当 SSM 位置 1 时,此位才有效。此位的值将作用到NSS引脚上,并忽略 NSS 引脚的 IO 值。

位 7 LSBFIRST:帧格式 (Frame format)

0:先发送 MSB

1:先发送 LSB

注意:正在通信时不应更改此位。

位 6 SPE:SPI 使能 (SPI enable)

0:关闭外设

1:使能外设

注意:2- 关闭 SPI 时,需按照后续介绍的指定步骤操作。

位 5:3 BR[2:0]:波特率控制 (Baud rate control)

- 000: fPCLK/2

- 100: fPCLK/32

- 001: fPCLK/4

- 010: fPCLK/8

- 011: fPCLK/16

- 101: fPCLK/64

- 110: fPCLK/128

- 111: fPCLK/256

注意:正在通信时不应更改这些位。

位 2 MSTR:主模式选择 (Master selection)

0:从配置

1:主配置

注意:正在通信时不应更改此位。

位1 CPOL:时钟极性 (Clock polarity)

0:空闲状态时,SCK保持低电平

1:空闲状态时,SCK保持高电平

位 0 CPHA:时钟相位 (Clock phase)

0:从第一个时钟边沿开始采样数据

1:从第二个时钟边沿开始采样数据 注意:正在通信时不应更改此位。