HSE时钟电路——皮尔斯(Pierce)震荡器

简介

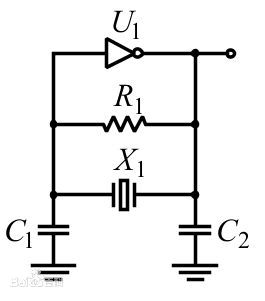

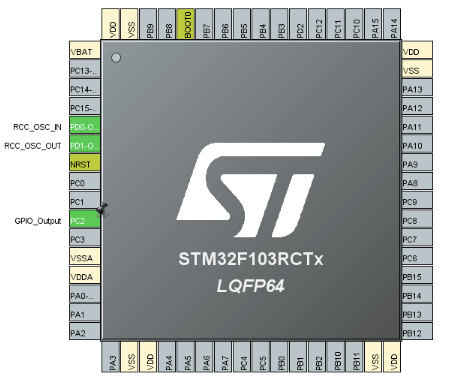

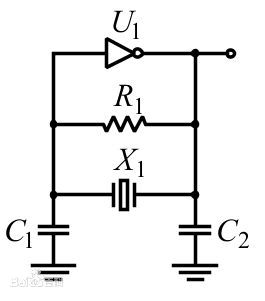

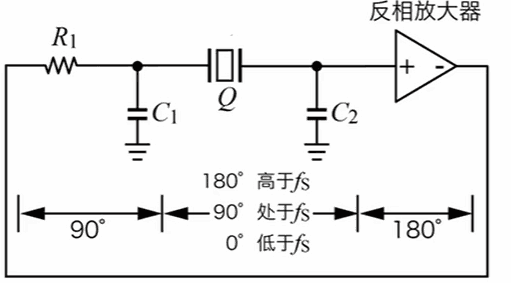

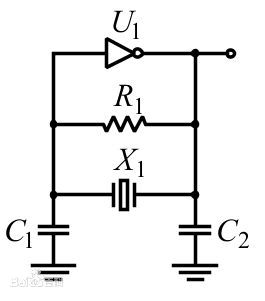

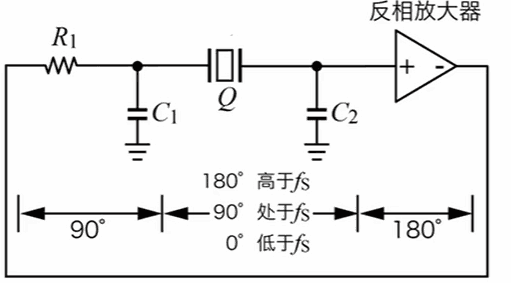

单片机上常见的HSE时钟——一个无源晶振配合两个电容的时钟电路,就是使用的皮尔斯振荡电路,其完整电路如下图,由两个电容 ($C_1\&C_2$) ,一个晶体振荡器 ($X_1$),一个反馈电阻 ($R_1$) 和一个反相放大器 ($U_1$) 组成。$U_1$和$R_1$一般集成在芯片内部,因此这就是在STM32中选择HSE(外部晶体振荡器)时钟时,有两个引脚 RCC_OSCIN 和 RCC_OSC_OUT 被占用的原因。

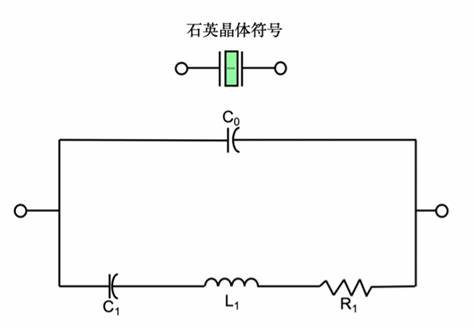

石英晶振的等效电路

在分析电路如何震荡之前,需要先了解石英的一个物理特性。

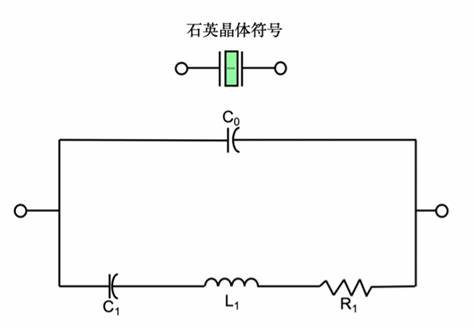

- 压电效应:当对压电材料施以压力时,能产生电;反过来,当给压电材料通电,能产生形变;因此,在石英晶体的两端施加持续变化的交流电压,即可让石英音叉形变“震荡”起来,物理的形变又回反过来改变电压,从某种意义上来说这也是一个储能元件。在计算上可以把晶振等效为一个RLC电路,如下图所示。其中$C_0$是石英晶体两脚间产生的寄生电容(一般取3-5pF),其余部分是晶振本身的等效RLC,也称为其“运动(Motional)参数”。

皮尔斯振荡器

如何进行选频

我们知道,振荡器会在反馈电路的谐振频率上进行振荡,这本质是反馈回路是一个滤波器,而谐振频率是反馈回路中电抗最小的时候。因此会将该频率进行无限放大,最后在此频率上震荡。

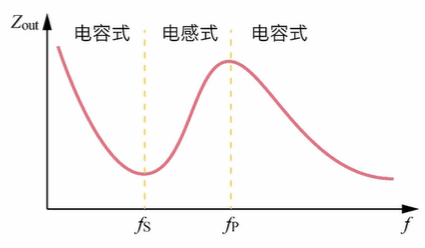

从上面等效电路我们可以看到,晶振有两个谐振频率:一个是$R_1,L_1,C_1$ 三个串联谐振的频率,称之为$f_s$;另一个是$R_1,L_1,C_1$ 与 $C_0$ 并联形成的电路的谐振频率,称之为$f_p$。

$f_s$频率就是串联电路感抗和容抗抵消,即:$2\pi f_sL_1=\frac{1}{2\pi f_s C_1}$,可解得:

$f_p$是串联电路感抗大于容抗,整个电路等效于一个电感的时候,和$C_0$发生谐振:

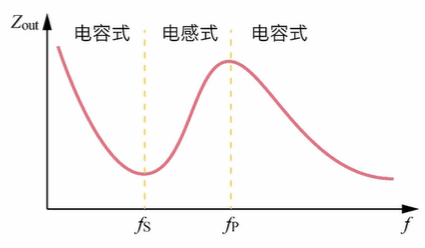

可以看出,当频率小于$f_s$时,$L_1$容抗非常小,整个电路的储能由$C_1$主导,因此呈容性(电压领先电流)。在$f_s-f_d$区间内,电路储能由$L_1$主导,因此呈感性(电压滞后电流)。而在频率大于$f_d$后,由于$C_0$支路电抗变小,因此主导支路变成了$C_0$而非$R_1C_1L_1$,再次呈现感性。

对不同频率呈现出不同的阻值,这就是一个滤波器。可以看出,这个滤波器对$f_s$附近的频率和$>>f_p$的频率通过性较好。

如何满足相位

在电子系统-振荡器一节中,我们提到,巴克豪森振荡准则是系统起振的必要不充分条件。那么皮尔斯振荡器是如何满足这个条件的呢?

观察下图,其可以被改写为另一种形式:

|

|

<<<<<<< HEAD

=======

building

其中$R_1$可以被理解为一个很小的等效电阻(当然也可以实际加一个电阻在这里)。

- 首先,反向放大器让信号相位旋转了180°。

- $R_1,C_1$让信号相位旋转了90°之间的任意一个值(取决于$R_1, C_1$的大小)。

- 如果晶振此时呈现感性(即,振荡频率满足$f_s90°。那么此时,总有一个频率会让相位一共旋转360°,满足巴克豪森震荡准则。

- 但是,如果振荡频率$ff_p$,晶振都将呈容性,那么相当于串联了一个电容,在加上电容$C_2$,整体相位移动会为0°。处于$f_s$时,晶振呈纯阻性,相位移动位于0-90°。

因此,一定有一个频率位于$f_s<f<f_p$之间,可让系统震荡。这也就是晶振震荡的频率。

至此,我们已经讨论了它滤波选频的原理和满足巴克豪森振荡准则的原理。

如何计算匹配电容

我们注意到,$C_1$和$C_2$两个电容是会影响相位的,而根据巴克豪森振荡准则,反只有相位为满足 $2n\pi$ 的信号才会起振,因此,$C_1,C_2$两个电容是会轻微影响震荡频率的(之所以是轻微影响,是因为它的影响范围在$f_s$到$f_p$之间,这个范围本就很小)。

晶振的供应商会给一个“负载电容” $C_L$,$C_L$的值是晶振本身决定的,当晶振外部等效电容等于$C_L$时,其输出的频率最准确。因此代入皮尔斯震荡电路,可以得到如下公式:

其中:

- $C_s$为电路板杂散电容和晶振引脚间电容,经验值取3-5pF.

如果让$C_1=C_2$的话:

至此便可计算$C_1$和$C_2$的值。

<<<<<<< HEAD

=======

building

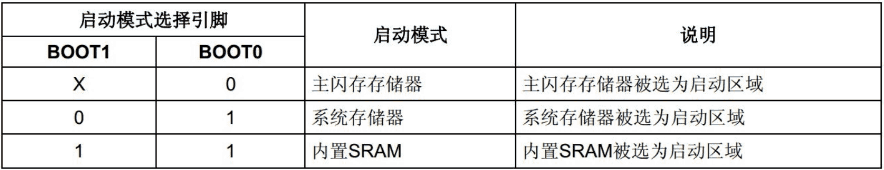

Boot选择器

三种Boot模式

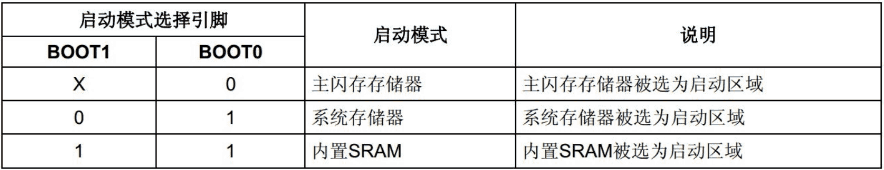

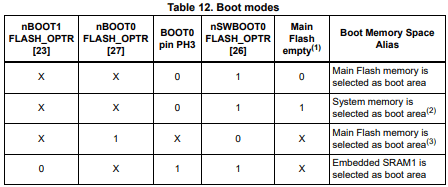

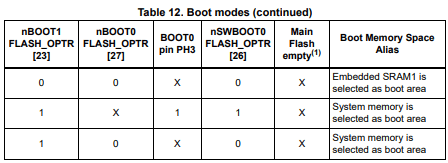

stm32有三种boot模式,分别使用boot0 和boot1引脚进行控制

主闪存启动

- 启动地址:0x08000000

- BOOT0: 0; BOOT1: X

这是STM32内置的Flash,一般使用JTAG或者SWD模式下载程序时,会写入到该区域内,重启后也直接从这启动程序。基本上都是采用这种模式。

系统存储器启动

- 启动地址:0x1FFF0000

- BOOT0: 1; BOOT1: 0

系统存储器是芯片内部一块特定的区域,STM32在出厂时,由ST在这个区域内部预置了一段BootLoader。ST公司的这一段Bootloader中提供了使用串口下载程序的固件。可以通过这个BootLoader将程序下载到系统的Flash中。通过串口下载程序步骤如下:

电脑通过 USB 转串口线连接 STM32 的 USART1,并打开电脑端的上位机;

- 接 BOOT0 为高电平,BOOT1 为低电平(选择 System Memory 启动);

- 复位单片机使其进入 bootloader 模式,此时串口可读取;

- 接回 BOOT0 低电平,BOOT1 低电平(选择 Flash启动);

- 复位单片机即可启动用户代码,正常运行;

SRAM启动

- 启动地址: 0x20000000

- BOOT0: 1; BOOT1: 1

SRAM没有存储程序的能力,一般用于程序调试。如果程序只进行了小修改,然后完全刷入flash,这个过程非常费时。而SRAM读写速度很快,可以在调试的时候使用。

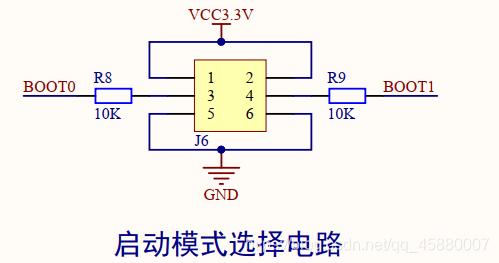

Boot选择电路

手动选择电路

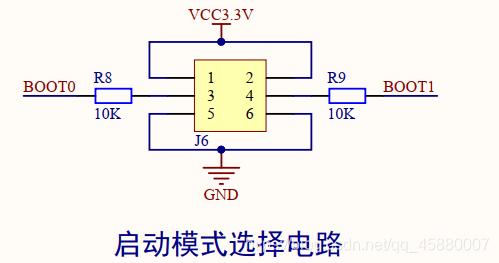

一般来说,我们用不到SRAM启动。因此通常BOOT1通过一个10K电阻下拉接地。

当然,也可以用跳线让用户自由选择,如正点原子的STM32战舰v3开发版。

这便是STM32的启动模式手动选择电路。

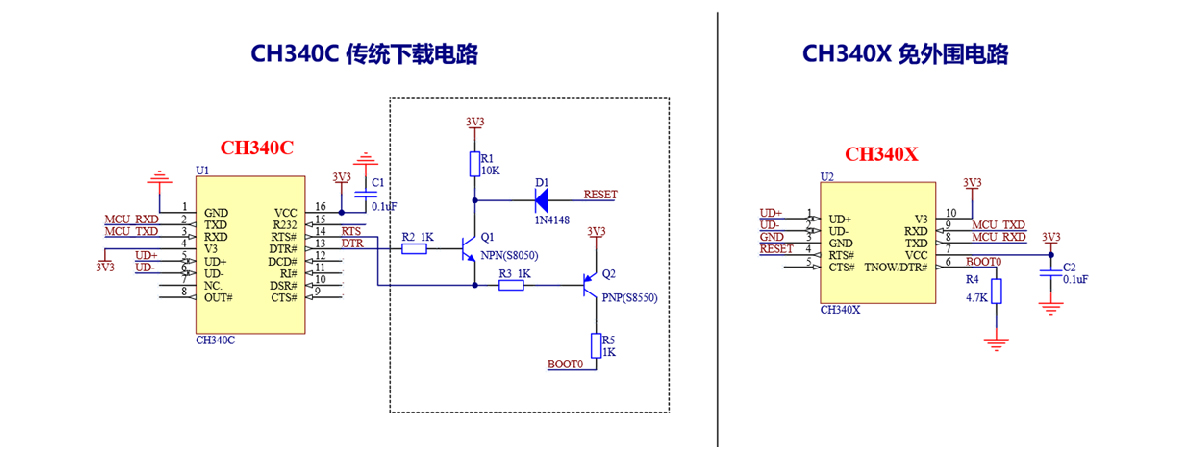

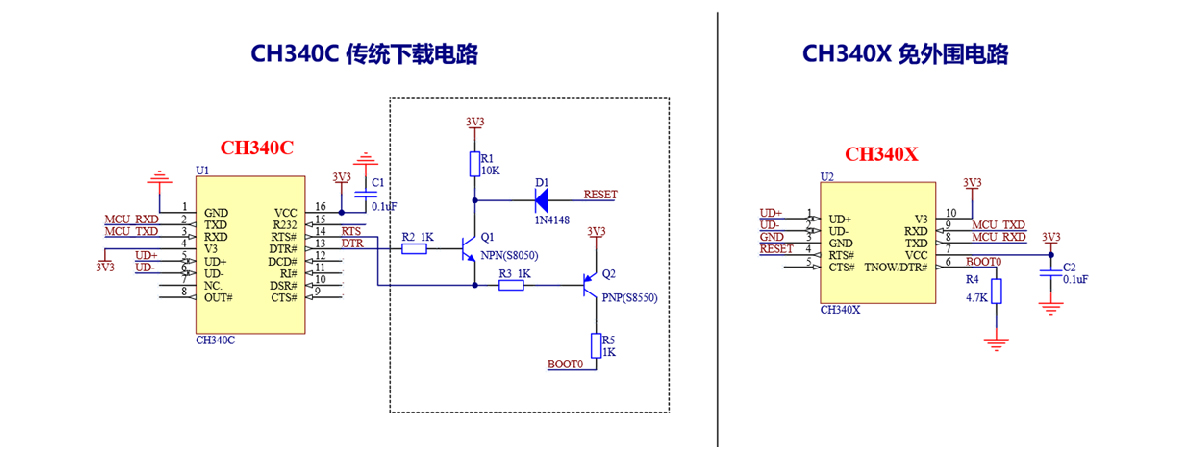

自动下载电路

STM32可使用CH340配合MCUISP进行ISP烧写,这其中的步骤是到以System Memory模式启动,烧录程序,再切换到Flash模式运行程序。通过CH340上的MODEM通讯引脚,可实现该操作。其原理请参考 CH340X+ISP烧录使用指南。

CH340与单片机连接如下,同时BOOT1通过一个10K电阻下拉接地。

配合MCUISP软件,该电路可以实现自动对Boot模式进行选择,然后通过串口下载程序。

此时CH340的RX需和STM32的USART1的TX(PA9)和USART1的RX(PA10)连接。

<<<<<<< HEAD

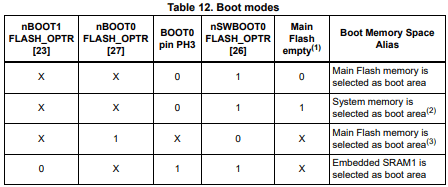

新版本:flash配置boot(以STM32L4+系列为例)

ST公司在部分产品上引入了一种全新的boot模式:仅使用一个实体BOOT引脚,配合FLASH内的配置比特来进行boot选择。这样可以实现程序自己切换boot模式。

首先,引入了如下几个比特:

- Main Flash empty:该比特由系统检测输出,用于判断用户的flash是否经过读写。flash空为1,flash有程序为0;

- nSWBOOT0 FLASH_OPTR:BOOT0引脚由实体引脚值决定还是flash内配置引脚值决定的选择比特。1:实体引脚决定,0:flash内nBOOT0值决定;

- nBOOT0 FLASH_OPTR:BOOT0引脚的flash内配置值。注意,其为NOT BOOT0(BOOT0取反),也就是该bit配置为1相当于实体引脚接0,该比特0相当于实体引脚接1;

- nBOOT1 FLASH_OPTR:BOOT1引脚的flash内配置值。注意,其为NOT BOOT1(BOOT1取反),也就是该bit配置为1相当于实体引脚接0,该比特0相当于实体引脚接1;

在nSWBOOT0为1时,BOOT0的值由实体引脚决定,此时:

- 若

Main Flash empty为1(即,flash内没有程序),且BOOT0配置为0(从flash启动),则不会遵循配置,而会强制从System Memory启动

- 其余时候遵循上面三种模式的BOOT表

官方给出的BOOT选择表如下:(一定要注意 nBOOT 是实体引脚值取反!)

=======

building

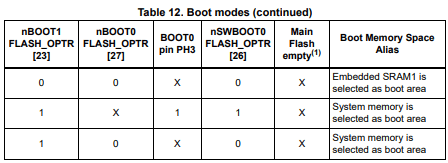

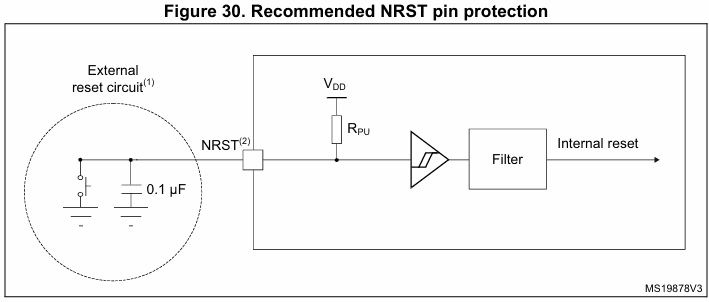

复位电路

STM32复位引脚为NRST,其复位引脚低电平有效,内部集成上拉电阻,因此无需外部上拉

官方推荐的复位电路如下:

可以看到,外部仅连接一个手动复位的按键和上电自动复位的电容。

<<<<<<< HEAD

=======

building

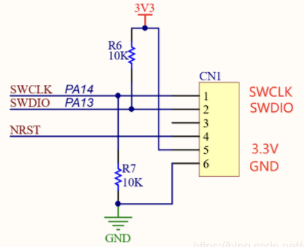

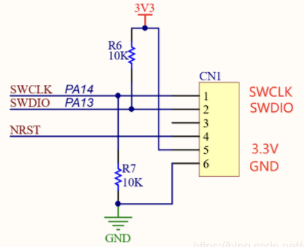

SWD下载电路

通常某宝买的盗版ST-Link,就是使用的SWD烧写。这种烧写方式只需要4根接线。 分别为VCC,GND,SWCLK, SWDIO。其中,SWCLK和SWDIO分别对应STM32上PA14和PA13引脚。

其中:

- SW协议规定,对于SWDIO,必须在电路板上进行上拉(ARM建议100KΩ)(虽然大部分板子都采用10KΩ上拉)。

- 对于SWCLK,芯片内部集成下拉,没有规定一定需要外部下拉。但是部分开发版依旧给了10K电阻的下拉。

因此,下载电路如下:

其中SWDCLK的下拉电阻可有可无,因为芯片内部已集成下拉。

通信电平转换电路

由于STM32使用的是3.3V CMOS电平,需要通过UART,I2C等协议与TTL设备(5V)通信时,尝尝需要进行通信电平转换。

版权声明: 本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 風!